近些年,汽车电子发展日新月异,功能越来越多,对处理器性能需求也越来越高,恩智浦新推出的高性能车辆网络处理器S32G2非常适合汽车中央网关。本文介绍了一些在S32G2硬件设计中需要注意的一些问题,包括电源设计、高速接口以及PCB Layout建议等。

分享链接:

本文介绍了一些在S32G2硬件设计中需要注意的一些问题,包括电源设计、高速接口以及PCB Layout建议等

为了能使客户更快的熟悉并应用S32G2,艾睿电子和恩智浦合作对该芯片进行了深度的前期开发,即将推出方便用户测试的开发套件SEED-S32G。

图 开发套件SEED-S32G

电源设计

S32G2芯片需要多种电源供给,包括核电源、IO电源、Fuses电源、模拟电源等,所有电源需要保证正确的供给,包括电压、最大电流、纹波,即使电源引脚相应功能没有使用,也需要保证正常供给。不过如果电源引脚对应功能没有使用的话,相关的去耦电容可以省去。

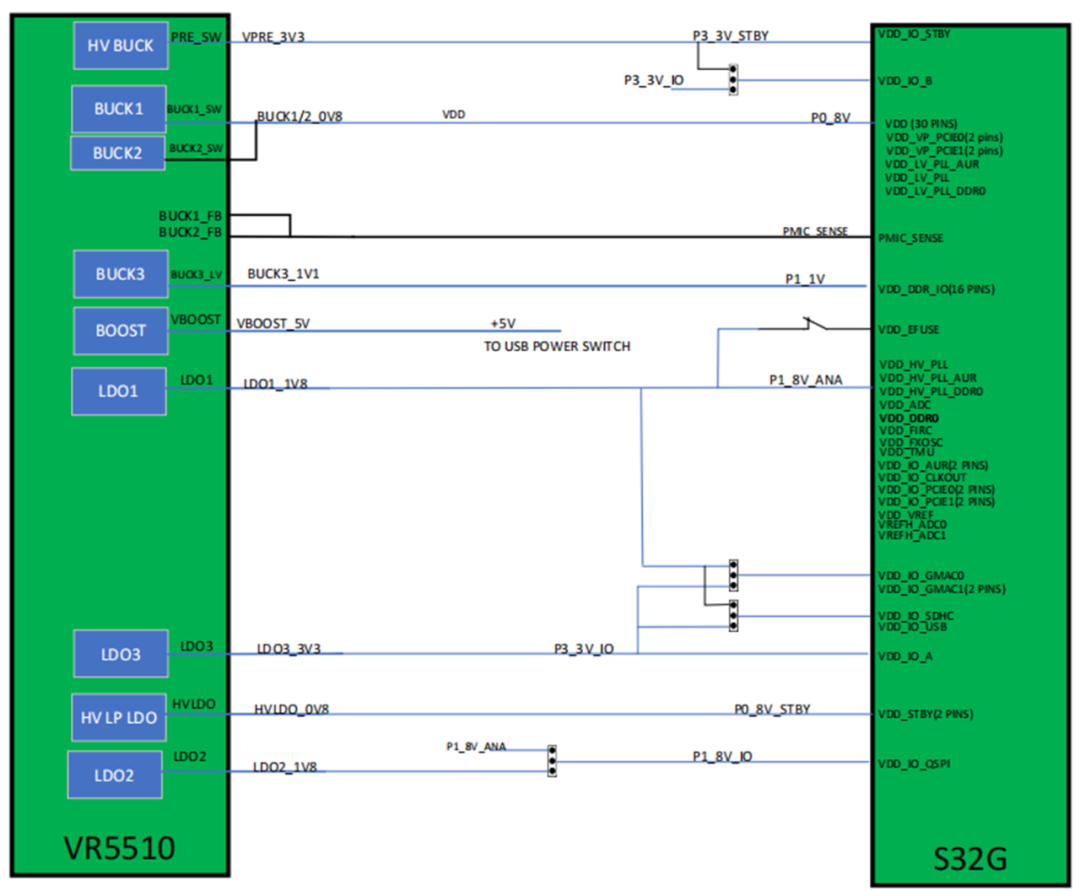

对于S32G2的电源,建议按照官方设计选用VR5510进行设计,这样可以加快件设计,同时也可以使得软件开发更方便,因为NXP官方SDK包提供了完整的VR5510支持。

电源连接

电源连接方式建议按照下图方式进行连接,其中部分电源有跳线选择,客户实际使用时可根据实际情况进行优化,确定选择其中一种电源,省去跳线电路。

旁路模式

对于PMIC来说,有下面两种旁路模式:

常规旁路模式:需要VPRE和HVLDO正常工作

带LPDDR4 自刷新旁路模式:需要VPRE、HVLDO、BUCK3以及LDO2正常工作

根据不同的需求,用户可以选择不同连接方式。S32G的VDD_IO_B可以选择是来自VPRE_3V3还是LDO3_3V3,其中的区别在于,在旁路模式下,VDD_IO_B是否需要供电,需要供电的话,就要连接到VPRE_3V3,如果不需要供电就要连接到LDO3_3V3。这里主要影响的是旁路模式下的功耗。由于CAN_Rx需要用于唤醒,所以处于VDD_IO_STBY电源域,但相应的CAN_Tx引脚处于VDD_IO_B电源域。

两种不同的设计分下面两种情况:

VDD_IO_B选择是来自LDO3_3V3,这样在旁路模式,CAN_Tx引脚处于不工作状态。

VDD_IO_B选择是来自VPRE_3V3,这种情况下,CAN_Tx引脚处于工作状态。这种情况下,S32G2在旁路模式多了40个工作的引脚。

旁路模式下工作的引脚如果有上拉,则会有0.3uA的漏电流产生。

旁路模式下不工作的引脚如果外部不是下拉或者不驱动,将会产生额外的漏电流。可以根据实际情况选择旁路模式是否给VDD_IO_B供电。

核电压配置

系统上电之后需要读一下S32G2芯片的DIE_PROCESS[1:0]寄存器,确定一下芯片的SVS模式是否有使能,如果有使能,即DIE_PROCESS[1:0] = 01b,需要把VR5510的SVS OFFSET[5:0]寄存器的值配置为 ‘0b00101’,从而将BUCK1/2_0V8的电压值配置为0.76875V,通过这种方式来优化功耗。

PMIC控制引脚连接

PMIC控制引脚与S32G2之间连接方式如下图所示:

其中I2C4可以替换为其他I2C引脚,只需修改软件配置即可。

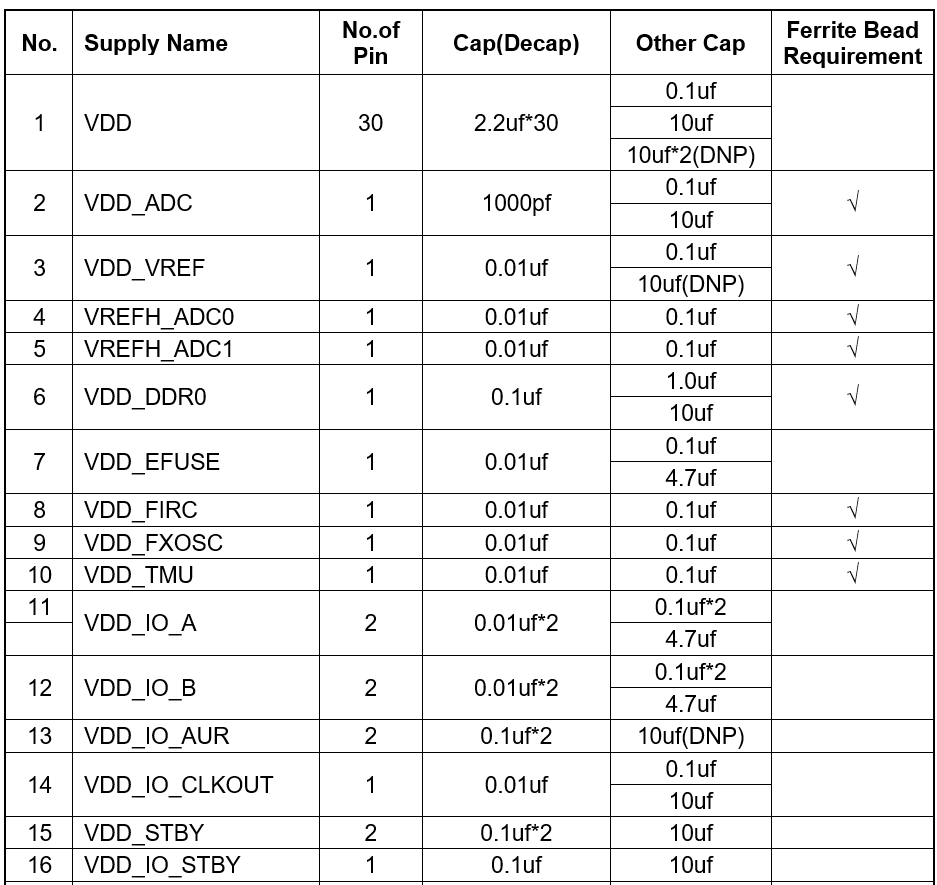

去耦及滤波电容设计

推荐按照下表进行电容选择:

S32G2的每一个电源引脚旁边都需要有一个去耦电容,其他电容可放置在磁珠旁。

去耦电容或者bulk电容需要距离电源过孔尽可能的近,最好不要超过50mils。其他的bulk电容可以放在BGA旁边。去耦电容距离芯片的电源引脚距离应足够近,这样有助于减少等效电感,从而保证芯片所需的高速瞬态电流。

VDD_EFUSE 设计

S32G包含一个Fusebox用于存储一次性烧写数据。在开发或者生产阶段烧写Fuse时需要给VDD_EFUSE引脚供电,其他时间段需要连接到地。这样可以保护Fuse被意外改写。如果硬件不需要修改fuse,可以将VDD_EFUSE引脚直接连接到地。

RESET 设计

芯片包含两个reset引脚,POR_B和RESET_B。

POR_B低电平有效,引脚内部包含一个弱下拉电阻。建议将改引脚连接至电源管理芯片的PGOOD引脚,并且搭配小于等于2kΩ的上拉电阻,这样芯片上电瞬间,电源管理芯片(VR5510)会将POR_B拉低,等所有电源电压稳定之后,电源管理芯片会释放POR_B。工作过程中,电源管理芯片监控的电源如果有异常,就会拉低POR_B,使芯片进入reset状态。POR_B引脚需要防止噪声干扰,引脚旁边可以加一个低通滤波电路。

RESET_B是一个开漏类型的双向引脚,内部包含一个弱上拉电阻。主要用于向外输出信号,用来指示芯片进入reset状态。其次,在调试芯片时,该引脚也可以用于reset信号输入。建议将RESET_B连接至电源管理芯片(VR5510)的RSTB引脚,并且外部加不大于10kΩ的上拉电阻。和POR_B引脚一样,RESET_B也需要防止噪声干扰,引脚旁边可以加一个低通滤波电路。

时钟设计

时钟源可选下面任一种:

EXTAL和XTAL引脚之间连接一个20/24/40 MHz的晶体

连接一个40MHz的单端时钟信号至EXTAL引脚

时钟的PCB设计需要参照以下规则:

由于内部已经集成,外部不再需要添加反馈电阻。

时钟电路越短越好。

VSS _FXOSC引脚直连到地平面。

PCB上的高频信号以及噪声敏感信号远离时钟电路。

S32G2 XTAL引脚旁的VSS引脚需要直连到地平面,并且和最近的VDD引脚之间需要通过电容连接。晶振两端需要放置电容,然后将电容直连地平面。

晶振周围可以在顶面放一圈地信号线来隔离噪声。

晶振下面放一块完整的地平面。

Boot 配置

Boot 相关引脚:

RESET_B释放时,BOOTMOD[0] (PA_02) 和 BOOTMOD[1] (PA_03)的电平状态会决定S32G2 的boot模式,RESET_B为低时,这两个引脚电平需要保持稳定。

BOOTMOD[0/1]引脚建议用1kΩ电阻上拉。

启动时,BOOTROM通过BOOTMOD和RCON引脚电平来决定不同的boot配置,这些引脚都是功能复用的引脚,启动之后都要用作其他功能。但是有些引脚,比如I2C功能的引脚使用时必须有上拉电阻,但是如果启动需要配置成低电平,这样就会有冲突,因此在开发板中增加了一个MAX4886ETO+芯片用于功能选择。等到产品量产阶段,可以通过烧写fuse来设置boot配置,MAX4886ETO+芯片就可以省去。

在开发阶段,启动配置BOOT_CFG有两个方法进行配置:从EEPROM读或者从32个GPIO RCON引脚读。

从EEPROM读取boot启动配置:

如果RCON8/PB_01引脚在RESET_B上升沿是高电平,boot配置会从EEPROM读取,这时,RCON7/PB_00会用作SDA,RCON8/PB_01会用作SCL。

EEPROM的I2C 地址需要设置为0xA0。

S32G2 会从EEPROM的0x0地址读前4byte的数据来配置RCON。数据格式为小端。需要按照RCON7-0 、RCON15-8、RCON23-16、RCON31-24的顺序存放数据。

当使用EEPROM作为RCON数据存放地址时,还需要烧写EEPROM用于S32G2的启动。

从GPIO读取boot启动配置:

Boot配置也可以在RESET_B上升沿从GPIO读取,需要通过外部的上下拉电阻来进行配置。GPIO RCON引脚如下表所示:

|

Signal Name |

Reset Config Bit |

|

PA_09 |

RCON0 |

|

PA_10 |

RCON1 |

|

PA_11 |

RCON2 |

|

PA_12 |

RCON3 |

|

PA_13 |

RCON4 |

|

PA_14 |

RCON5 |

|

PA_15 |

RCON6 |

|

PB_00 |

RCON7 |

|

PB_01 |

RCON8 |

|

PB_02 |

RCON9 |

|

PB_03 |

RCON10 |

|

PB_04 |

RCON11 |

|

PB_05 |

RCON12 |

|

PB_06 |

RCON13 |

|

PB_07 |

RCON14 |

|

PB_08 |

RCON15 |

|

PB_09 |

RCON16 |

|

PB_10 |

RCON17 |

|

PB_11 |

RCON18 |

|

PB_12 |

RCON19 |

|

PB_13 |

RCON20 |

|

PB_14 |

RCON21 |

|

PB_15 |

RCON22 |

|

PC_00 |

RCON23 |

|

PC_01 |

RCON24 |

|

PC_02 |

RCON25 |

|

PC_03 |

RCON26 |

|

PC_04 |

RCON27 |

|

PC_05 |

RCON28 |

|

PC_06 |

RCON29 |

|

PC_07 |

RCON30 |

|

PC_08 |

RCON31 |

Debug接口

S32G2包括一个标准JTAG接口和高速Aurora调试接口。

Input/Output 引脚

下表总结了S32G2的引脚类型

引脚复用

S32G2的多数引脚都可以用作多种功能。可以通过软件选择配置为哪种功能,详细功能可参考S32G2用户手册附件的IOMUX文件。

注入电流

所有的引脚都内置了保护二极管。一些应用中,数字和模拟引脚都有可能连接到高于工作电平的电压,比如由于不同器件或者不同板卡上电顺序的原因。这种情况下,只要是器件是断电的,就可以支持电流注入。不过等到上电之后,用户还是需要保证引脚工作电平不要超过最高限值。

引脚外部可以增加额外的高速ESD保护器件。

未使用引脚

未使用的可以悬空,软件配置成输入以及禁用输出buffer,(SIUL2 MSCR bits OBE and IBE =0) 、内部上拉使能 (PUE = 1)

CLKOUT_P、CLKOUT_N、 POST_AN是NXP内部测试引脚,需要悬空

TMU_ANODE以及TMU_CATHODE,接地。如果实际情况不方便实现,可以悬空。

所有未使用的ADC输入需要下拉到地

S32G2 仿真模型

下面几种模型可直接从NXP官网下载并用于仿真:

IBIS Model

BSDL Model

DDR S-parameters Model

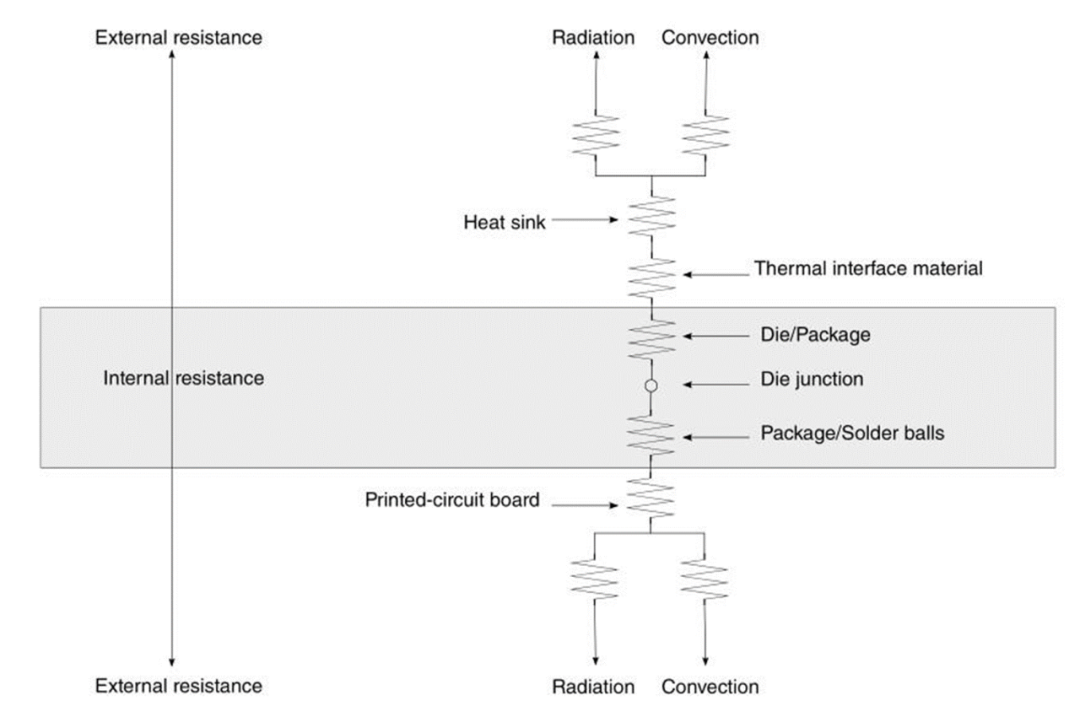

S32G2 散热

散热管理需要综合考虑各种因素。可以通过热仿真来分析系统的散热性能。最常用的散热方式是散热片,直接贴装于S32G2上即可。散热设计需要考虑下面几个方面:

保证留给散热片足够的空间

温度敏感器件不要放置在散热片下

注意散热片槽的方向,保证热空气快速流走

S32G2导热路径路径如下图所示,大部分的热量都通过散热片发散。

S32G2 布板布线设计

NXP 官方开发板使用Allegro设计。用户如果使用其他工具的话,可以进行格式转换,不过需要注意,转换完成之后,可能会出现部分错误,需要手动调整。

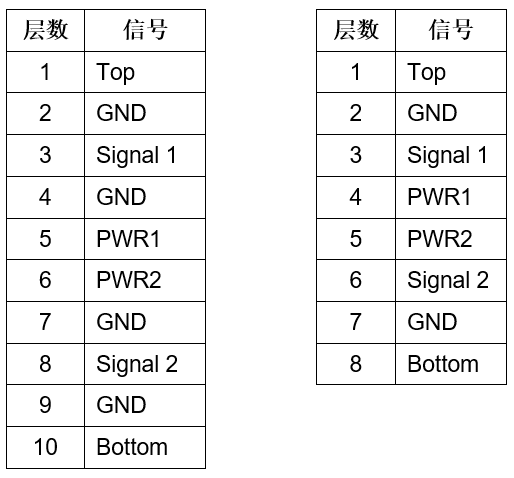

层叠设置

由于S32G2 引脚比较多,推荐至少8层板设计,层叠设置对于高速信号的质量比较关键,高速信号需要有临近的参考平面来减少串扰。下面两种层叠设置可供用户参考。

高速信号走线设计:

优先走高速信号

走线做需要的阻抗控制

高速信号不要穿过参考平面间隙

高速信号过孔旁放置地过孔

晶体下面放置地平面

同步信号接口走线做合适的等长

PCB材质

PCB材质通常需要关注两个参数:介电常数和介质损耗因子。选材时最好选适合高频应用的材料。介电常数一般来说会随着信号频率的提高而降低。而高频材料在一个很宽的频率范围(100MHz~几GHz)都有相对稳定的介电常数以及相对较低介质损耗因子。介质损耗因子越低,信号功率损耗越低。

通常来说,FR4板材介质损耗因子会在0.02-0.01之间,而高速板材介质损耗因子会在0.009-0.002之间。FR4板材介电常数会在4.2-4.5之间,高速板材介电常数会在3.7-3.3之间如何通过layout降低PCB板材对信号完整性造成的影响?

信号线尽可能短,高速信号线层紧挨其参考平面,地平面紧挨电源平面,如果可以的话,高速信号尽量走顶层和底层,因为顶层和底层比内层有更低的传输延迟。

新板卡首次上电

这部分内容介绍一下,新板卡第一次上电注意事项。

首先,意外的大电流会损坏板卡,上电之前先用万用表测量各个电源对地阻抗,看是否有短路情况。第一次上电尽量使用带限流功能的电源,并观察实时电流。

上电之后首先测量所有电源是否在正常范围,防止出现过高电压损坏器件。运行一个大负载程序,然后再测量一次所有电源是否正常。

如果有启动问题需要确认下面几个问题:

确认POR_B信号在所有电压都正常之前一直处于拉低状态

POR_B拉高之前保证EXTAL/XTAL引脚晶振或者晶体正常工作

各个电源符合datasheet上电时序的要求

以上是S32G硬件设计中关于电源、时钟、启动、布局布线等一些设计注意事项,下一篇文章我们将介绍关于S32G2 Memory 以及高速接口的设计。

MyArrow™ — 艾睿电子线上系统

MyArrow™ — 艾睿电子线上系统