接 NXP S32G2 硬件设计篇(上),下篇里我们将介绍关于 S32G2 的 Memory 以及高速接口的设计。

分享链接:

下篇里我们将介绍关于 S32G2 的 Memory 以及高速接口的设计。

DDR

S32G2既可以外接LPDDR4也可以外接DDR3L。如果不使用外部DRAM,相关引脚可以悬空。(需注意S32G234M不支持DRAM接口)。

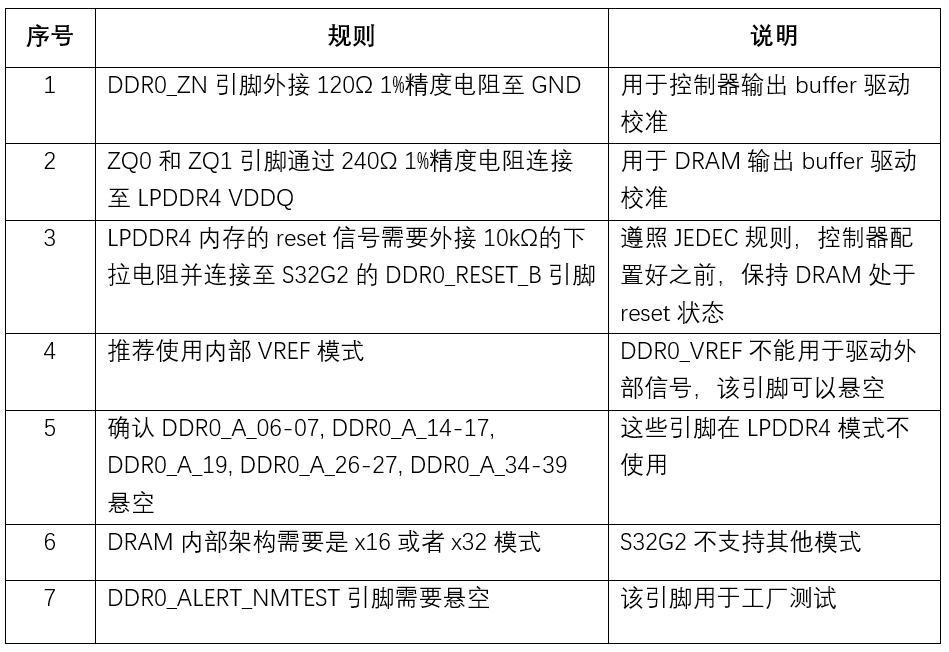

如果外接LPDDR4,需要按照下表规则:

数据线调序

在PCB layout 时,有时为了方便走线,需要调整接线方式,调整时需要按照如下要求:

首先,在LPDDR4系统中,信号按照下列方式分组

• Channel A: Byte0 and Byte1, CA_A[5:0], CKE0_A, CKE1_A, CS0_A, CS1_A

• Channel B: Byte2 and Byte3, CA_B[5:0], CKE0_B, CKE1_B, CS0_B, CS1_B

其中每组Byte内部的数据线,可以在组内随意调换位置;

一个channel内的Byte 直接可以整体调换(如Byte0可以和Byte1整体调换,但是Byte0和Byte3不可以调换)。

LPDDR4 Layout规则

同一组的DQ信号需要在相同的层。

DQ信号线上有过孔的话,过孔旁边可以放置地过孔,提高屏蔽能力以及保持阻抗连续

所有信号阻抗都到参考地平面。

走线不要经过分割的平面。

单端信号线阻抗设计为40 Ohm (+/-10%),差分信号线阻抗设计为80 Ohm (+/-10%)

信号线间距至少2倍于信号线到参考平面的距离,不同组之间的信号线间距以及到差分线的间距最好保持至少3倍。保持足够的距离只参考平面边缘。

信号线上尽量少的使用过孔,单根信号线最好不要超过2个。同组信号线保持相同的过孔数。在做等长计算时,过孔长度也需要考虑进去。

最大走线长度和拓扑结构、驱动能力、终端等都有关系。

地平面需要提供低阻抗的返回路径。

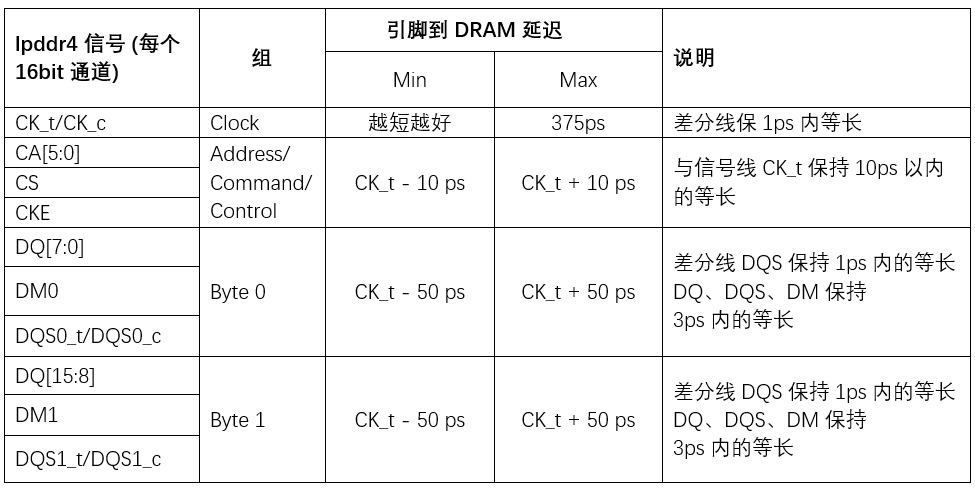

走线规则按照下表要求

当使用DDR3L时需要按照下面规则

数据线调序

和LPDDR4类似,在PCB layout 时,有时为了方便走线,也可以调整接线方式,调整时需要按照如下要求:

每组Byte内部的数据线,可以在组内随意调换位置

一个channel内的Byte 直接可以整体调换

DDR3L Layout 规则

DDR3L layout时需要遵照下面规则:

VREF_DDR以粗线的方式进行走线

CK/CK#需要按点对点的方式从控制器走到DRAM,并且等长。单端信号线阻抗控制为50Ω,差分线阻抗控制为100Ω

ADD/CMD 需要按照T型拓扑走线,并且在末端通过40Ω的终端电阻连接至VTT。

ADD/CMD 阻抗在终端电阻之前控制为40Ω,终端电阻之后控制为50Ω,T型拓扑的分叉点需要尽可能靠近DRAM。

同组数据线保持等长,并尽量在同一层走线,单端信号线阻抗控制为50Ω,差分线阻抗控制为100Ω。

QSPI

QuadSPI 接口可以外接一个或者两个外部flash(通过QSPI A 和QSPI B接口),每个都支持8位双向数据线。

QSPI_A只支持1.8V,QSPI_B支持1.8V或者3.3V。QSPI_B和SDHC接口复用相同的引脚。对于1.8V的QSPI flash设备,如果有连接RESET_B,则需要一个电平转换芯片,因为S32G2的RESET_B是3.3V的电平信号。

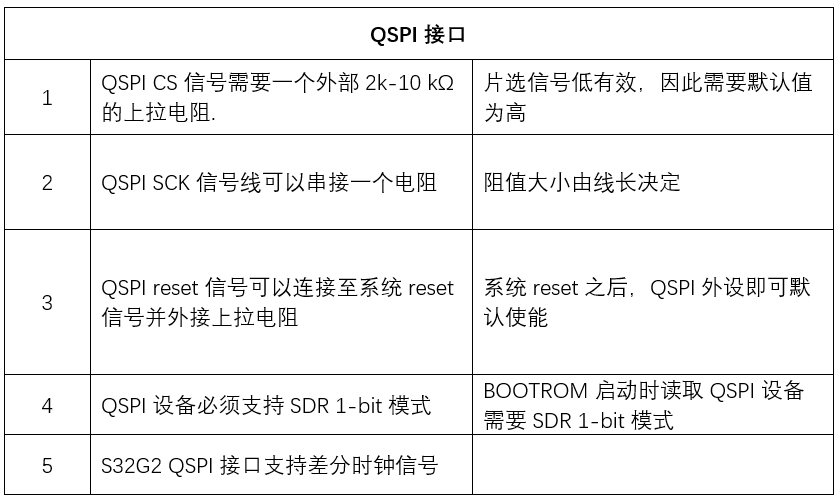

QSPI设计指导

QSPI Layout 规则

DQ信号线(包括RWDS)最大线长和负载容值相关

总的负载容值需要小于15pf,总容值包含以下几种:

走线电容(FR4板材大约3.3pf/inch)

器件封装引脚电容

和过孔相关的寄生电容

所有走线需要做+/- 50 mils 以内的等长

以太网

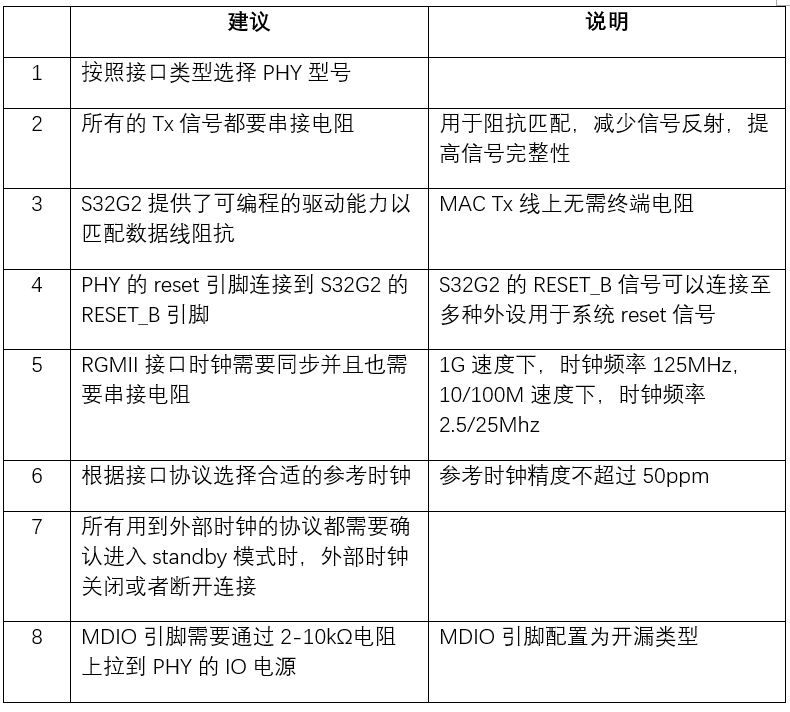

以太网设计有以下设计建议:

RGMII信号走线时需要按照下面规格:

Tx信号组合Tx信号组分别置于相同层

走线避免90度拐角

MAC到PHY走线长度不超过3 英寸

走线间距大于等于3倍线宽

所有 TX、TXCLK、RX、RXCLK信号做到组内+/-50 mil的等长

RJ45金属外壳连到机壳地,从而减少EMI

MDI信号线对按照差分方式走线

SerDes

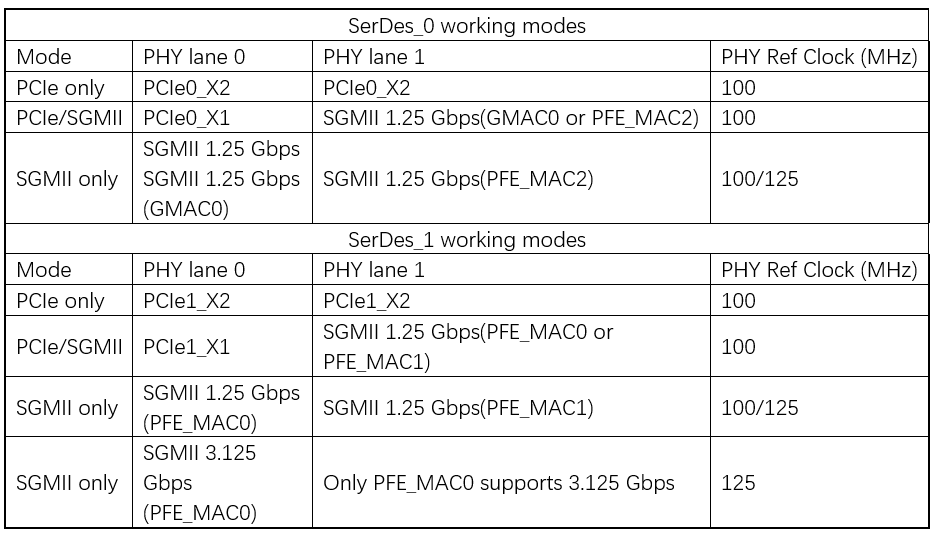

S32G2有两个SerDes接口,每个都可以配置为PCIe或者SGMII。S32G234M上只支持PCIe_0。下表展示了可选的SerDes配置方式:

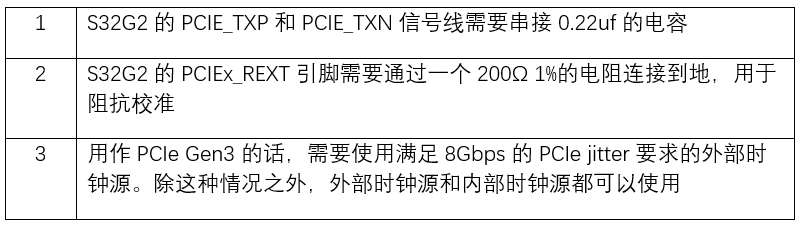

PCIe 设计推荐按照下面规则:

SGMII 设计推荐按照下面规则:

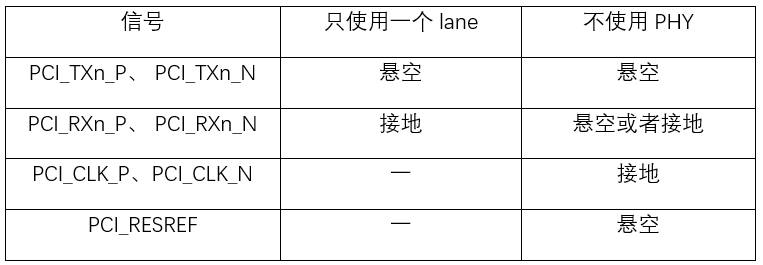

未使用引脚设计

SerDes布线按照下面规则:

走线参考平面需要连续,不要经过平面分割槽,放置连接器时,保证地平面包围每个引脚

PCIEx_REXT信号走线尽可能短

差分信号线不要走晶振下面,也不要平行于时钟走线以及数据信号线

差分线设计为100Ω 阻抗,并尽可能短

线宽和间距在整个走线过程中不要改变

差分线对的长度差距在5mil内

差分线两根线过孔数量及规格保持一致,并且过孔对旁边放置距离相等的地过孔

USB-ULPI

USBOTG符合USB2.0协议,可以作为主设备、从设备或者OTG设备。速度支持HS、full-speed(FS) 和 low-speed(LS),S32G234M不支持USB-ULPI。

开发套件SEED-S32G即将推出,敬请期待:

MyArrow™ — 艾睿电子线上系统

MyArrow™ — 艾睿电子线上系统