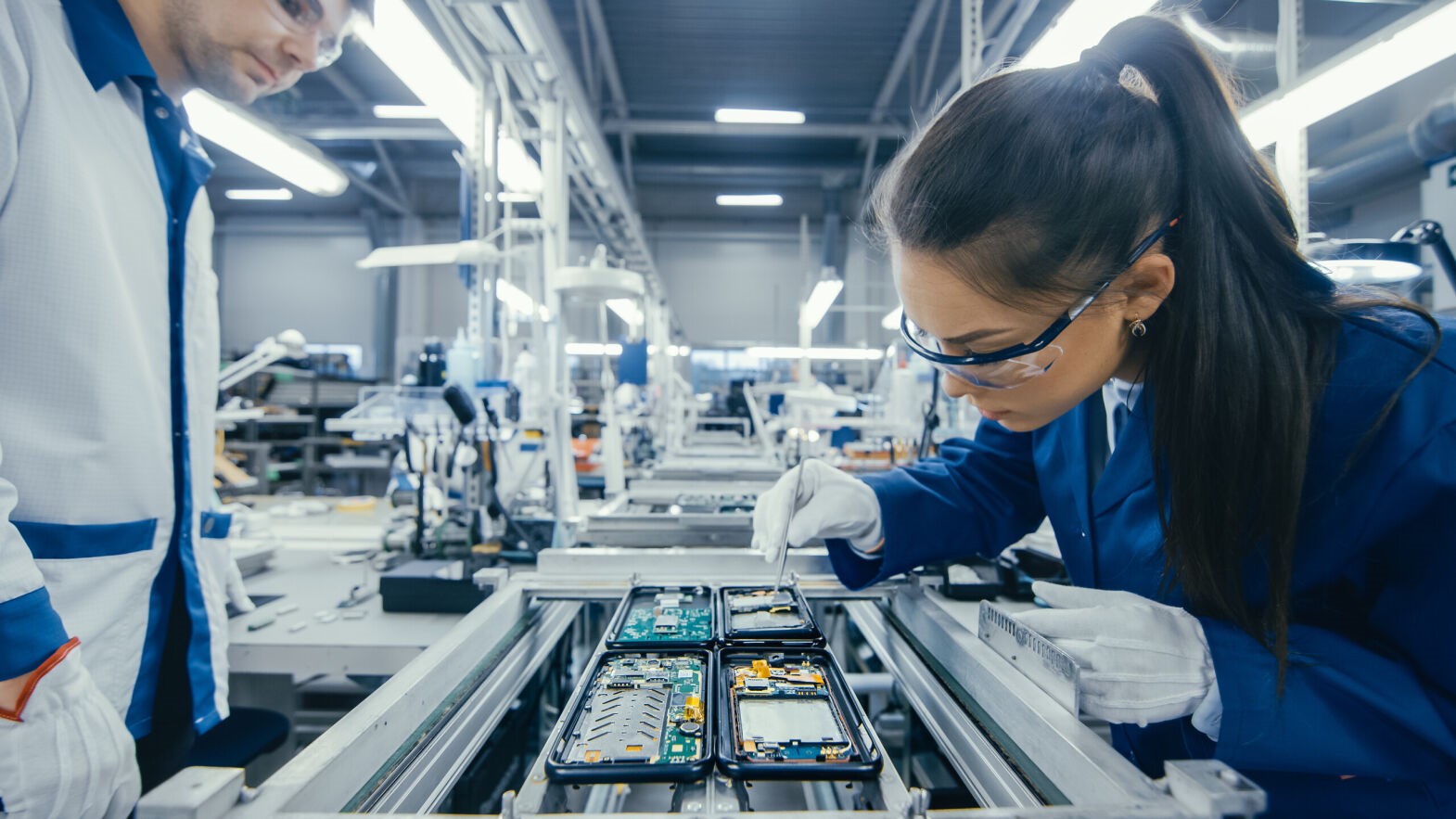

边缘人工智能 (AI) 处理应用,需要快速处理,并安全管控信息,推动了高度集成处理器的进一步发展,增强了NXP在应用处理器方面的投入。NXP在处理器这块耕耘了很多年,从早期的i.MX 6 → i.MX 7 → i.MX 8,再到最新的i.MX 9都已经有一条完整的生态链以及很多客户基础。大家通过下图可以看到NXP i.MX系列CPU的完整路线图。

NXP在处理器这块耕耘了很多年,从早期的i.MX 6 → i.MX 7 → i.MX 8,再到最新的i.MX 9都已经有一条完整的生态链以及很多客户基础。

边缘人工智能 (AI) 处理应用,需要快速处理,并安全管控信息,推动了高度集成处理器的进一步发展,增强了NXP在应用处理器方面的投入。NXP在处理器这块耕耘了很多年,从早期的i.MX 6 → i.MX 7 → i.MX 8,再到最新的i.MX 9都已经有一条完整的生态链以及很多客户基础。大家通过下图可以看到NXP i.MX系列CPU的完整路线图。

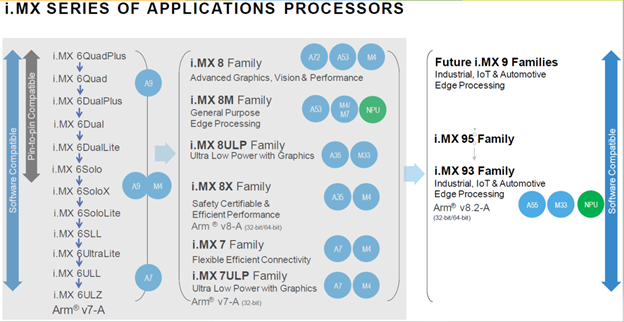

i.MX 93是NXP i.MX9产品组合中最新的一个系列。i.MX 93可以为边缘系统提供强劲的推理能力,可以快速处理传感器数据,并在保证安全的同时快速做出决定。该系列产品具备可扩展性,性能兼容性等特点。

i.MX 93的简单Block Diagram见下图,接下来将会给大家介绍i.MX 93的主要功能。

1. i.MX 93是双核Cortex A55,Cortex A55的性能要比Cortex A53的性能提升1倍,在测试一些整数18%、浮点38%、渲染14%、综合21%的性能增加。

2. i.MX 93继续沿用多核异构的架构,2*A55+Cortex M33,但是与以往不同的地方在于:I.MX 93可以从任一内核启动,工业很多客户需要快速启动或者低功耗的需求。比如从M核运行,A核关掉,后者M核启动等。这样做的目的主要是为了MCU可以帮助客户做一些实时交互处理,达到降低CPU的功耗。

至于如何实现从任意一个核启动的原理,给大家做下详细的介绍。

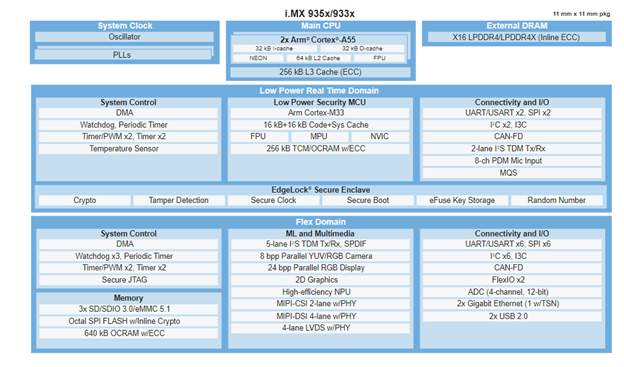

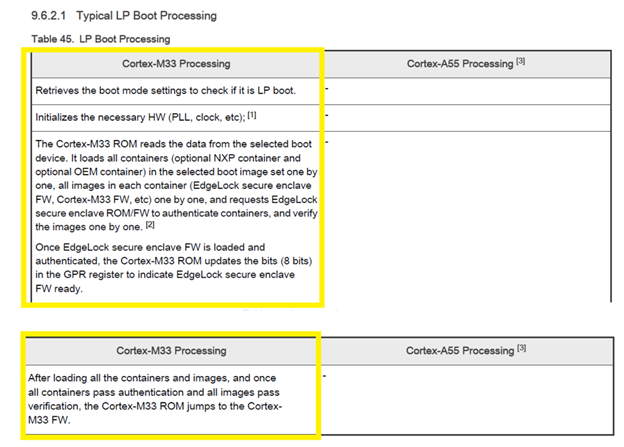

i.MX 93任意核启动分两种方式启动,一个是Single Boot(A55核先启动)和Low Power Boot(M33先启动),如何配置成Single Boot and Low Power boot,详见下图的Boot Type Selection表格,主要是通过Boot Mode Pin去做选择。

1). 比如选择A55核启动后,可见Reference manual 9.6.1.1 single Boot processing启动过程,大家注意一点,A55更新完寄存器状态后,A55核会通过MU发送一个message后才会启动M33核,详见下图。

2). 如何从M33核启动,可以见Reference Manual 手册9.6.2.1 LP Boot Processing的章节,有关于启动的完整流程图,见下图

3. 2*CAN FD接口,很多工业客户也需要用到CAN FD接口,其实CAN到CAN FD只是升级协议,物理层未做改变,传输速率不同、数据长度不同、帧格式不同、ID长度不同。CAN FD提高位速率的同时提供更短的CAN帧,CAN FD可以在CAN帧中容纳从8到64字节更多的数据,CAN FD具有更高性能的CRC算法。

4. 8*UART/USART接口, 串口上面会比i.MX8Mmini/8MPLUS要多些,对工业和医疗领域需要更多UART口的话是一个福音。很多工业和医疗客户板间通信以及外挂一些模块,都需要用到UART接口,如果不外挂就只能依靠外部的MCU的UART。NXP在i.MX 93上面延续了i.MX6ULL的8个串口的优点。

5. 2*Ethernet, 2x Gb Ethernet: AVB & IEEE 1588 for sync, and EEE for low power. 1 with TSN。这里要提到的是TSN(时间敏感网络),它主要特点是确保网络数据传输的时间确定性以及保证数据在准确的时间内以最小的时间抖动进行传输。

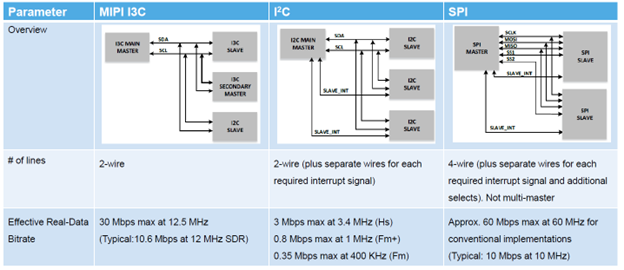

6. I2C and I3C,随着移动设备上传感器数量的增加,总线上数据量的增加,I2C的速度已受到限制,功耗也相对大些,以下是I2C/I3C/SPI接口速率和特性的对比(按照MIPI I3C, I2C, SPI标准的定义做的对比)。

7. 另外提到一点Up to 3.7GT/s x16 LPDDR4/LPDDR4X (with Inline ECC),这里一个是DDR速率可以做到最高3.7GT/s,内部带有ECC保护,ECC主要是错误检查和纠正,能够提高运行的稳定性和增加可靠性。

8. i.MX 93的GPU,PXP 2D 加速器, 支持支持YUV 422、420、444和任何RGB格式的像素等特点。LCDIF显示,LDB and 4-lane LVDS 显示 (up to 1366x768 or 1280x800),Parallel display (up to 1366x768 or 1280x800),一个 4-lane MIPI-DPHY DSI Tx PHY 和MIPI-DSI 控制器。

9. 机器学习: Arm Ethos U-65 Neural Processing Unit (NPU) 可以实现每个周期256个MAC。主要是用于入门级的机器学习, 硬件加速器管道化程度更高,NPU利用率更高。相关详细NPU的介绍可以参考NXP reference manual 手册Chapter 18 Neural Processing Unit (NPU)。

借助提供配套的软件工具和技术支持,强劲而丰富成熟的硬件能力赋能客户能更好地拿模型,数据,快速优化,验证并部署i.MX 93到系列新的边缘运算应用场景,是入门级边缘应用的理想选择。

MyArrow™ — 艾睿电子线上系统

MyArrow™ — 艾睿电子线上系统