今天将介绍S32K3硬件设计中需要注意的一些问题,包括电源设计、旁路电容、晶体、PCB Layout以及不同系列兼容性等。

介绍S32K3硬件设计中需要注意的一些问题,包括电源设计、旁路电容、晶体、PCB Layout以及不同系列兼容性等。

今天将介绍S32K3硬件设计中需要注意的一些问题,包括电源设计、旁路电容、晶体、PCB Layout以及不同系列兼容性等。

电源设计

S32K3芯片需要外部来供给的电源一共有三种:VDD_HV_A、VDD_HV_B以及V15,其中VDD_HV_A和VDD_HV_B电平可以相同也可以不同,V15既可以通过外部NPN三极管产生也可以由外部SBC供给。

VDD_HV_A = VREFH = VDD_HV_B = +5.0V,V15 = +1.5V(外部NPN三极管)

VDD_HV_A = VREFH = VDD_HV_B = +3.3V,V15 = +1.5V(外部NPN三极管)

VDD_HV_A = VREFH = VDD_HV_B = +5.0V,V15 =+1.5V (SBC)

VDD_HV_A = VREFH = VDD_HV_B = +3.3V,V15 =+1.5V (SBC)

VDD_HV_A = VREFH = +5.0V,VDD_HV_B = +3.3V,V15 = +1.5V(外部NPN三极管)

VDD_HV_A = VREFH = +5.0V,VDD_HV_B = +3.3V,V15 = +1.5V (SBC)

对于VDD_HV_A和VDD_HV_B,每一个引脚都应放置一个尽可能近的旁路电容(100nf-220nf),同时在电源入口的地方还应放置一个4.7uf-10uf的电容;对于V15,以及之前没有提到的V11、V25(内部产生,无需外部供给),每个引脚需要放置一个1nf以及100nf电容,另外V11、V15还需要外加一个2.2uf电容;V15如果是用NPN产生的话,需要确认所选NPN三极管型号能否满足系统最大功耗问题;对于VSS以及VREFL应该连接到同一个地平面;VDD_HV_A、 VDD_HV_B、以及V15还应满足上电以后上升时间的要求。

需要注意的是对于5V IO 和3.3V IO 的支持的最快翻转速度不一样的。VDD_HV_B电源域主要是Ethernet,QSPI SAI等高速IO 应用,如果配置到5V,速度会受一定影响。

V15主要是给内核供电。比起常规的MCU只有一个3.3或者5V然后内部LDO降压给内核供电(一般1.1V),K3单独一个V15就是为了减少压降,从而使内核更好地散热。如果不给V15供电,芯片也是可以工作的,但是只能工作在低功耗模式,如果需要内核正常全速工作,V15通过外部供给是必须的。

时钟设计

S32K3 包括以下几个时钟源:

8 - 40 MHz Fast External Oscillator (FXOSC)

48 MHz Fast Internal RC oscillator (FIRC)

32 kHz Low Power Oscillator (SIRC)

32 kHz Slow External Oscillator (SXOSC)

Up to 320 MHz System Phased Lock Loop (SPLL)

FIRC和SIRC属于内部时钟,硬件设计无需注意。对于外部时钟可以参考下图:

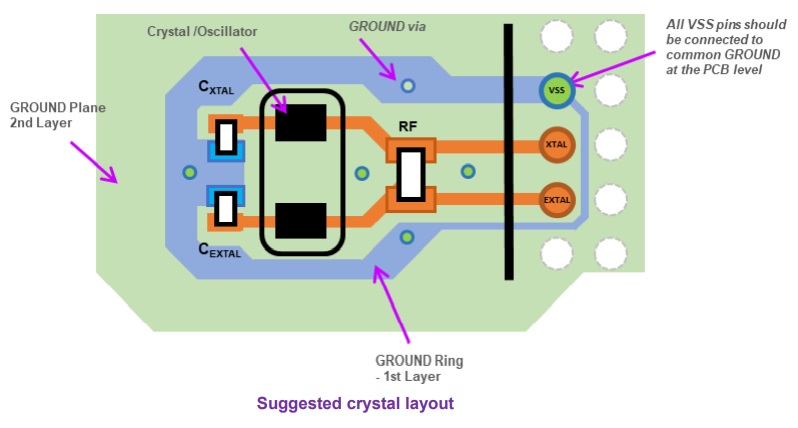

其中元器件参数可以参考所选晶体的说明。晶体与芯片之间连线应尽可能短,尽量不适用过孔。其他信号线,特别是时钟线、模拟信号线以及频繁开关的信号线尽量远离晶体。晶体下方应有一块完整地平面,同时晶体周围可以铺一圈地信号。最后一点晶体匹配电容接地点应尽量短并且最好对称布局。Layout可以参考下图。

调试接口设计

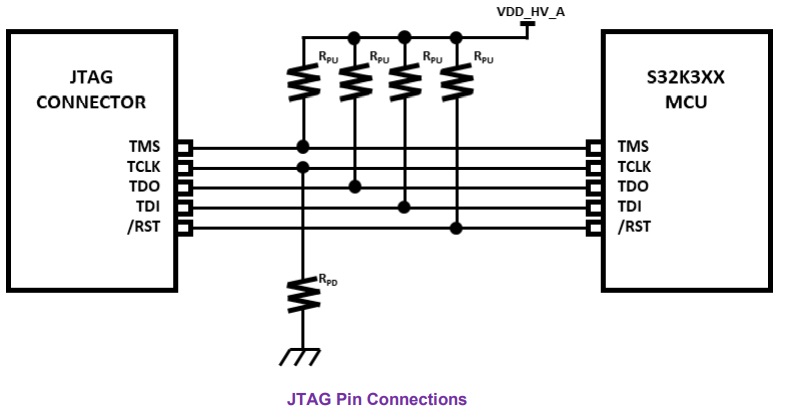

S32K3调试接口采用标准的JTAG接口,如下图所示。

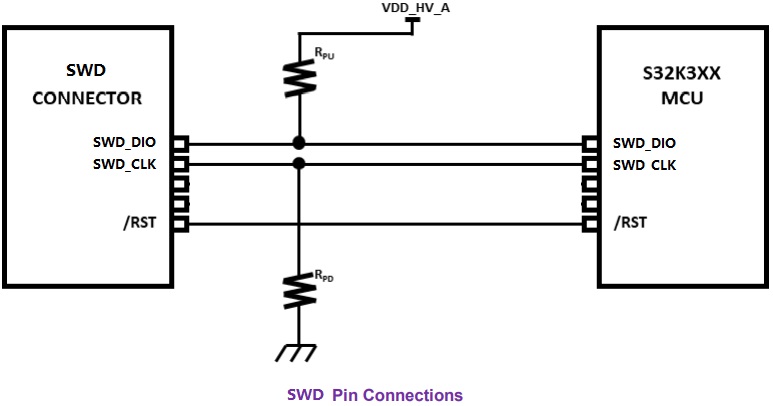

对于实际使用,可以使用下图中SWD模式,这样可以使得调试接口所需引脚更少,电路更加简单。

未使用的引脚处理

未使用的引脚可以按照下表中的建议进行处理:

Layout 建议

1. 信号线建议

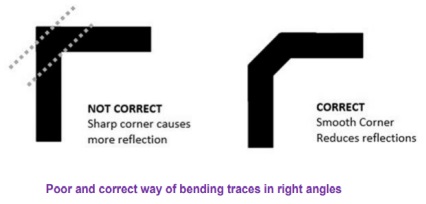

直角的走线会引起更多的辐射,同时直角区域的寄生电容会增加,阻抗特性也会改变,阻抗的改变会产生信号的反射,因此走线应避免直角,可以通过两个45°角来代替,如下图所示:

2. 地信号建议

为避免串扰,两层信号层之间建议加一个地平面层;高速信号应位于一个完整的地平面上;如果高速信号需要通过过孔来改变走线层,过孔旁边应放置一个地过孔;地平面不要分割为模拟地、数字地以及电源地,应该铺成一个完整连续的地平面;避免出现浮铜,浮铜需要用多个过孔与地平面相连,如下图所示:

EMI/EMC以及ESD

EMI可以有多个产生源,PCB、连接器、线缆等。其中PCB是最主要的产生源,PCB的EMI可以来自于很多方面:信号线的数字信号、电流回环区域、不合适的电源滤波系统、传输线效应、没有足够的电源和地平面、采用PWM方式控制的电源等。每个板子或者系统在EMI/EMC以及ESD方面的问题都会不一样,需要单独考虑。但是我们有一些通用的注意事项可以减少一些不必要的电磁干扰:

确保电源设计与实际的应用相匹配并且采用最优的去耦电容

电源端提供合适的滤波电容,滤波电容的等效电感应尽量低

走线层空间足够的话,铺一些地平面,并把这些地平面通过过孔连接到地平面层

电流回路尽可能小,并添加尽可能多的去耦电容

保证高速信号远离其他信号,特别是远离输入输出端口或连接器

S32K3芯片所有引脚内部都内置了ESD保护二极管,规格可以参考芯片datasheet的相应章节。

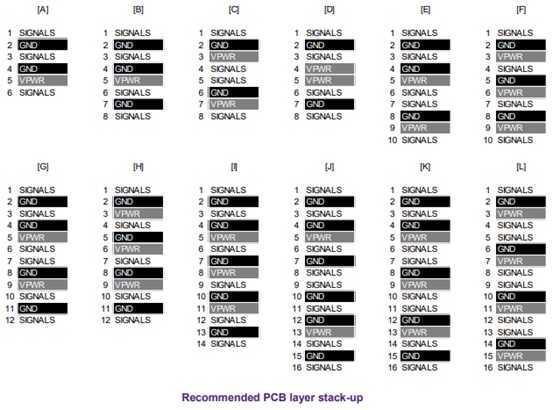

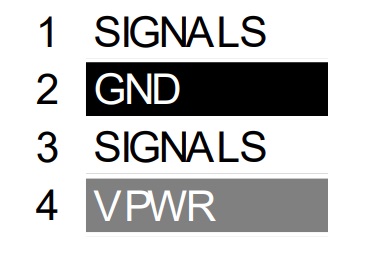

PCB层叠设置

NXP官方给出了不同层数PCB的推荐设置,如下图所示

不过,对于非BGA封装的S32K3芯片,其实4层板是完全足够进行设计的,层叠设置如下图所示:

兼容性设计

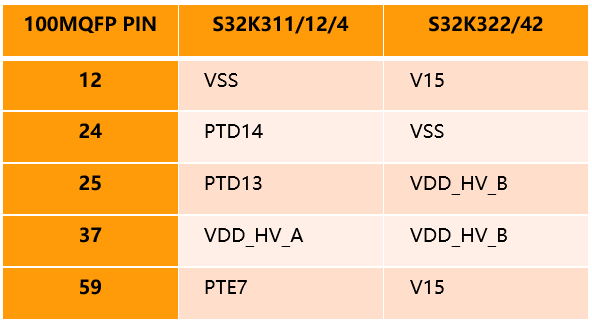

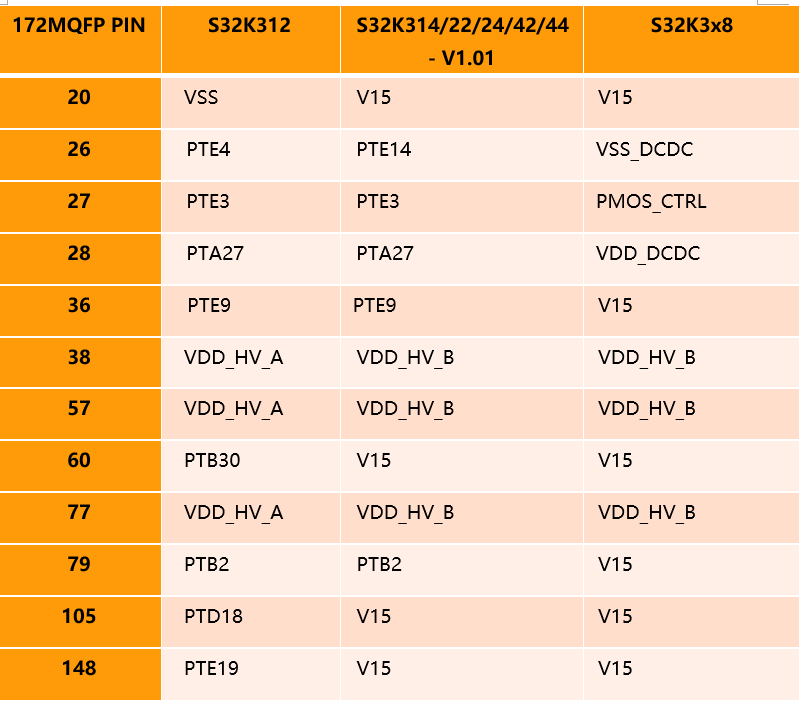

S32K3系列有很多不同的型号,相同封装不同型号芯片的引脚定义基本一致,但是如果您设计的产品希望能够兼容不同型号的话,还是有一些地方需要注意。

首先,可以看下面这个列表:

如果颜色相同的话,就表示引脚定义完全一致;如果颜色不一样的话,就表示引脚定义不一样。

对于100MQFP封装的型号,大家可以参照下表。设计时,把以下引脚通过0欧电阻进行进行兼容设计即可。

对于172MQFP封装的型号,大家可以参照下表:

MyArrow™ — 艾睿电子线上系统

MyArrow™ — 艾睿电子线上系统